Digital-Design-and-Computer-Architecture-第六章归纳

0 前言

这一章主要学习MIPS架构,黑书的结构感觉有点混乱,所以按一定的逻辑重新组织了一下各个部分的内容。这一篇笔记类似于“字典”的形式,方便复习或查阅。

1 Four Principles in MIPS Design

- Simplicity favors regularity.

- Make the common case fast.

- Smaller is faster.

- Good design demands good compromises.

2 Three Operands

Register Set/Register File

| Name | Number(5 bits) | Use |

|---|---|---|

| $0 | 0 | the constant value 0 |

| $at | 1 | assembler temporary |

| $v0-$v1 | 2-3 | function return value |

| $a0-$a3 | 4-7 | function arguments |

| $t0-$t7 | 8-15 | temporary variables |

| $s0-$s7 | 16-23 | saved variables |

| $t8-$t9 | 24-25 | temporary variables |

| $k0-$k1 | 26-27 | operating system (OS) temporaries |

| $gp | 28 | global pointer |

| $sp | 29 | stack pointer |

| $fp | 30 | frame pointer |

| $ra | 31 | function return address |

Memory

Organization Pattern

MIPS uses a byte-addressable memory.

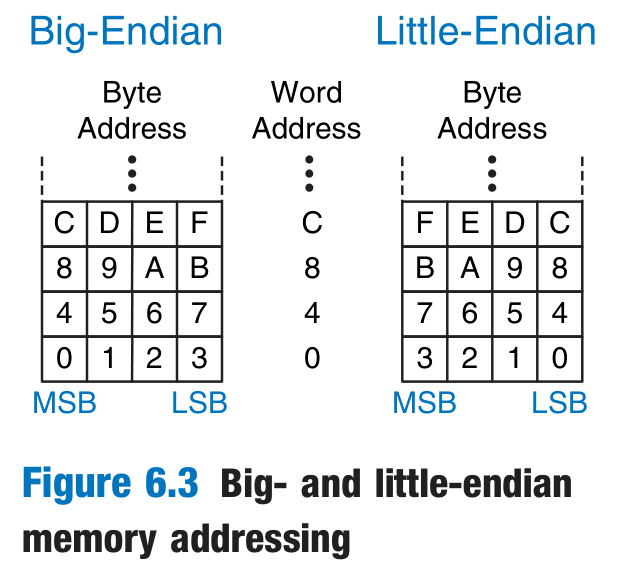

Big-Endian and Little-Endian:

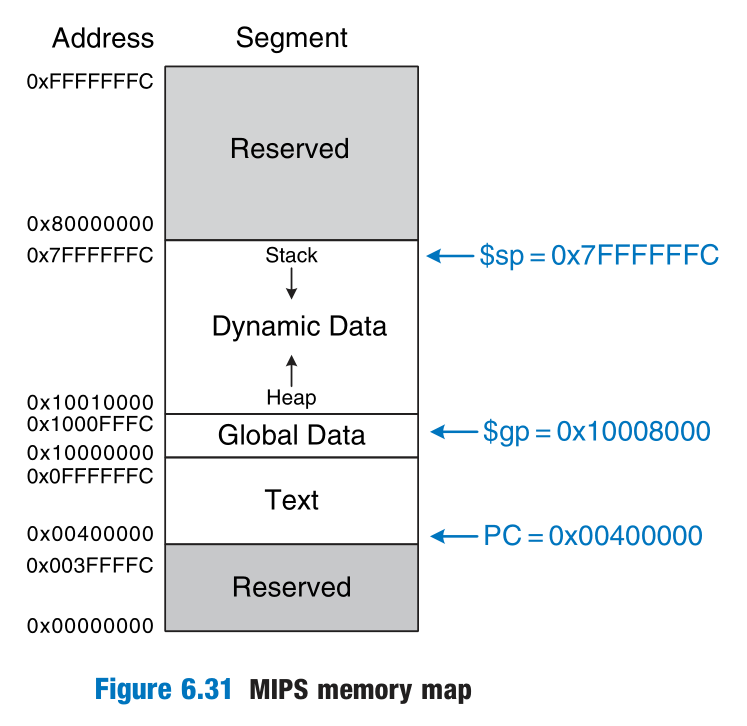

Memory Map

Constants/Immediates

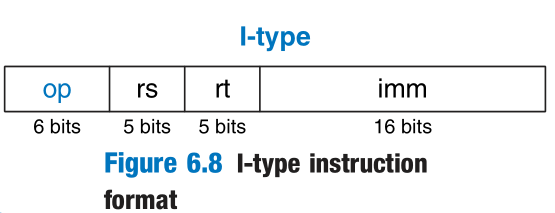

The immediate specified in an instruction is a 16-bit two’s complement number in the range [–32,768, 32,767].

3 Instructions Set

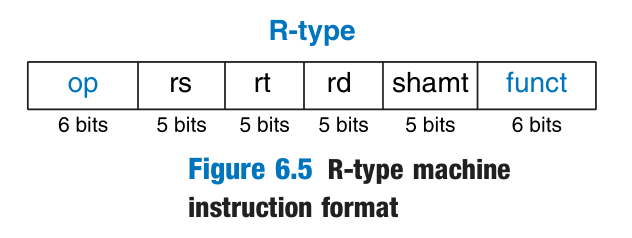

R-Type

Instruction Format

I-Type

Instruction Format

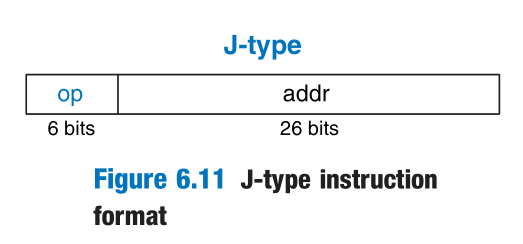

J-Type

Instruction Format

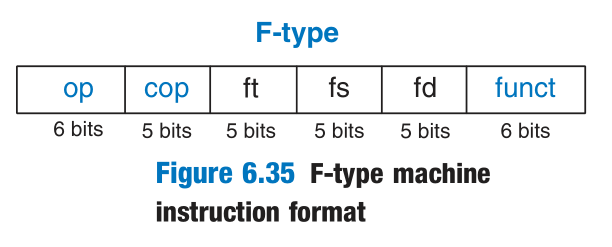

F-Type

Instruction Format

Addressing Modes

Register-Only Addressing

Register-only addressing uses registers for all source and destination operands. All R-type instructions use register-only addressing.

Immediate Addressing

Immediate addressing uses the 16-bit immediate along with registers as operands. Some I-type instructions, such as add immediate (addi) and load upper immediate (lui), use immediate addressing.

Base Addressing

Memory access instructions, such as load word (lw) and store word (sw), use base addressing. The effective address of the memory operand is found by adding the base address in register rs to the sign-extended 16-bit offset found in the immediate field.

PC-Relative Addressing

Conditional branch instructions use PC-relative addressing to specify the new value of the PC if the branch is taken. The 16-bit immediate field gives the number of instructions between the BTA and the instruction after the branch instruction.

Pseudo-Direct Addressing

The J-type instruction encoding does not have enough bits to specify a full 32-bit JTA. Fortunately, the two least significant bits, $JTA_{1:0}$, should always be 0, because instructions are word aligned. The next 26 bits, $JTA_{27:2}$, are taken from the addr field of the instruction. The four most significant bits, $JTA_{31:28}$, are obtained from the four most significant bits of PC + 4. This addressing mode is called pseudo-direct.

Because the four most significant bits of the JTA are taken from PC + 4,

the jump range is limited.

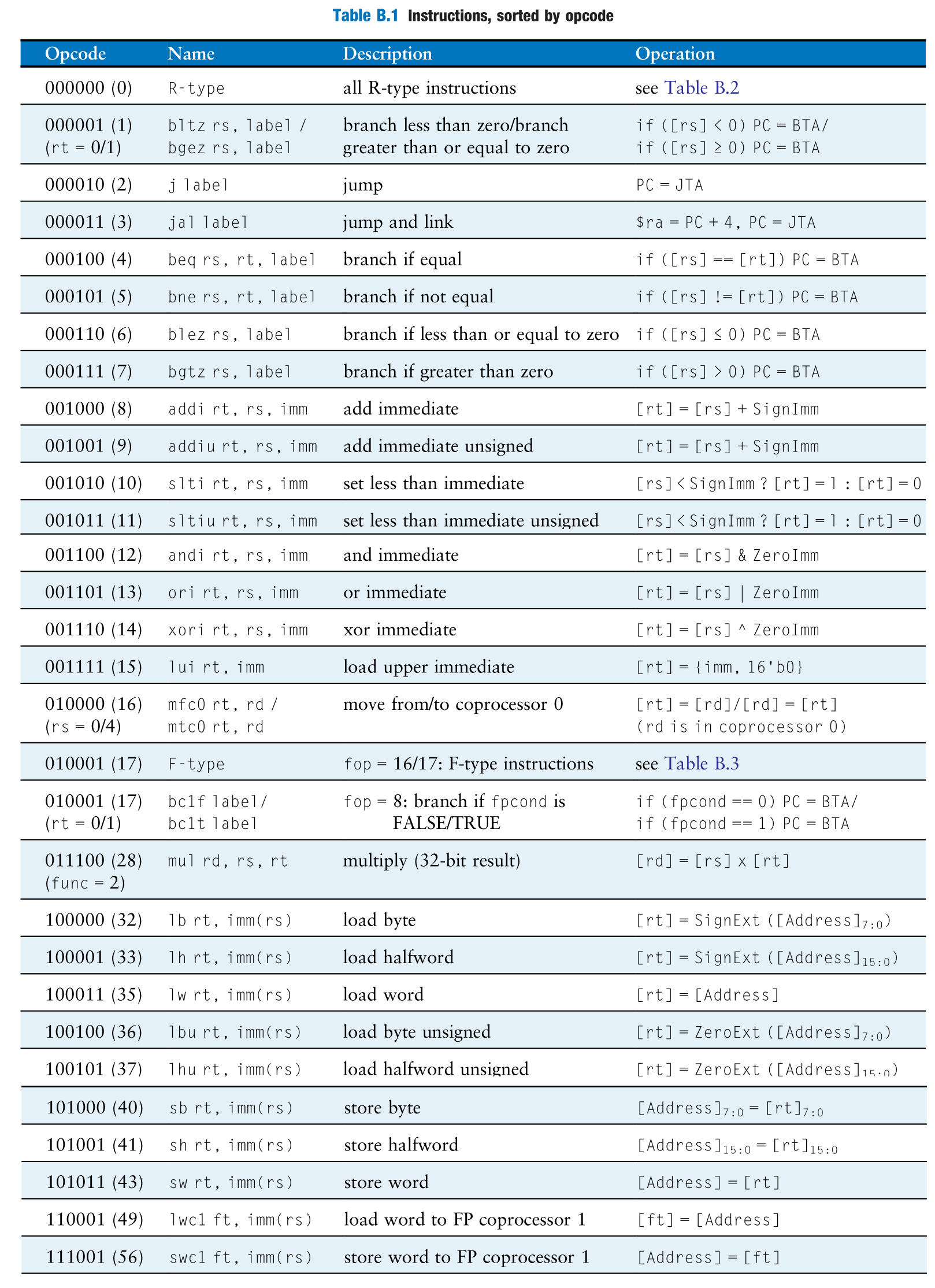

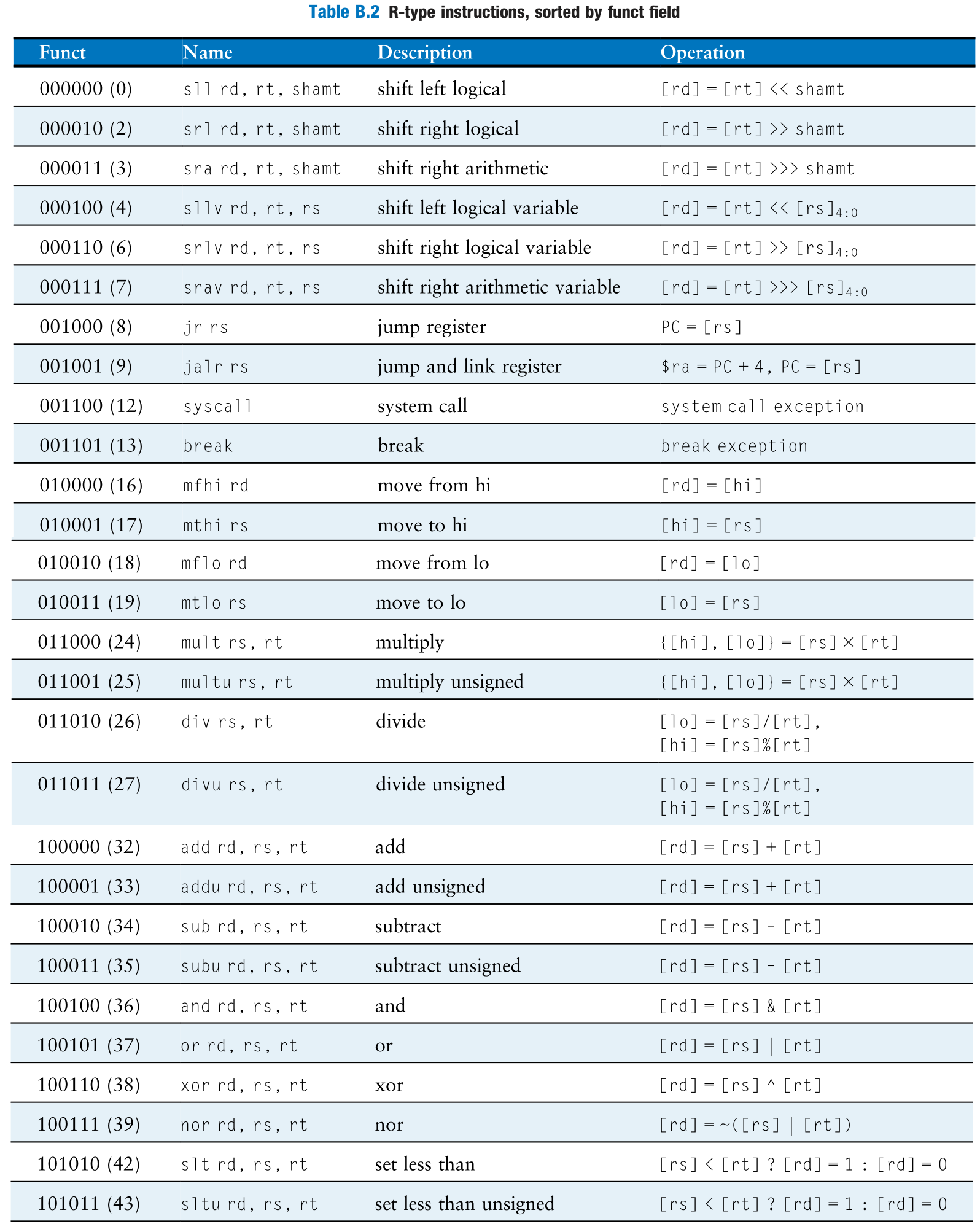

MIPS Instructions Tables

4 Programming

32-Bit Constant

The and instruction is useful for masking bits.

The or instruction is useful for combining bits from two registers.

A NOR $0 = NOT A.

1

2

3

4

5

6

7

8

9# 32-BIT CONSTANT

# High-Level Code

int a = 0x6d5e4f3c;

#MIPS Assembly Code

# $s0=a

lui $s0, 0x6d5e

ori $s0, $s0, 0x4f3c

Conditional Statements

if Statement

1 | # High-Level Language |

if/else Statement

1 | # High-Level Language |

switch/case Statement

1 | # Hight-Level Language |

Loop Statement

while Loop

1 | # High-Level Language |

for Loop

1 | # for Loop |

Function

Example 1

1 | # High-Level Language |

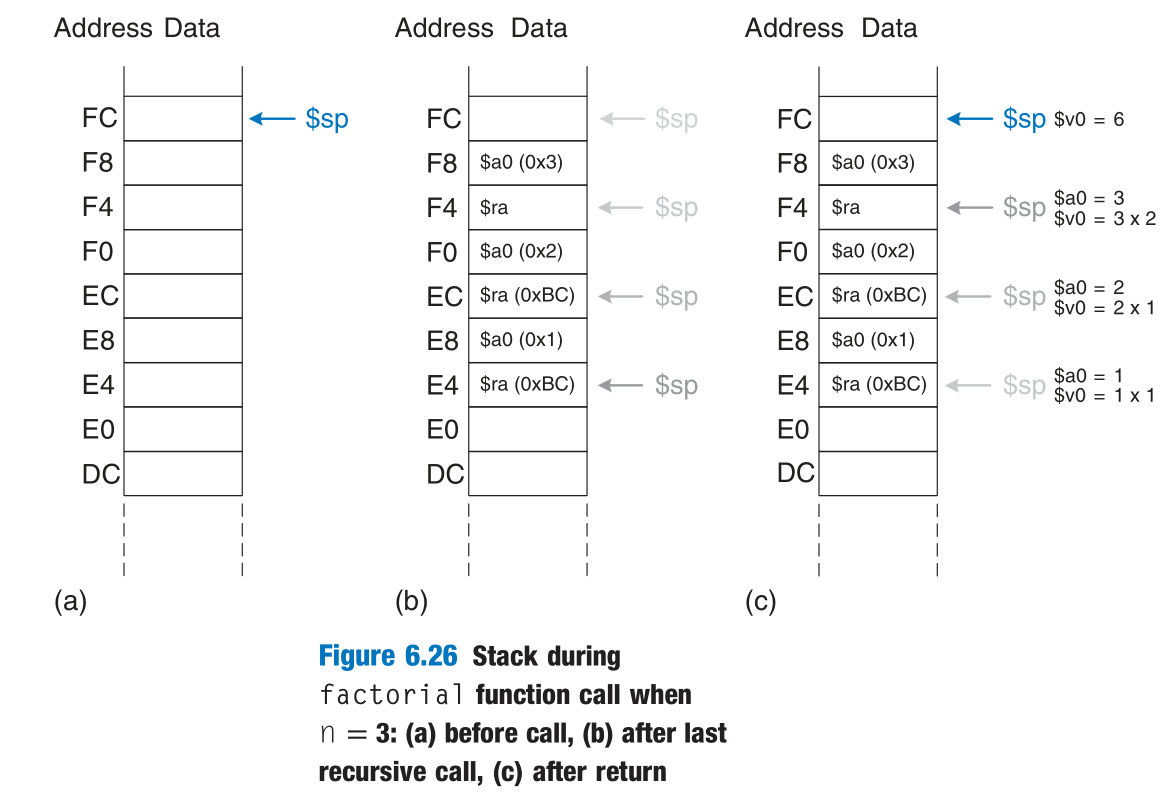

Example 2 (Recursive Function)

1 | # High-Level Language |

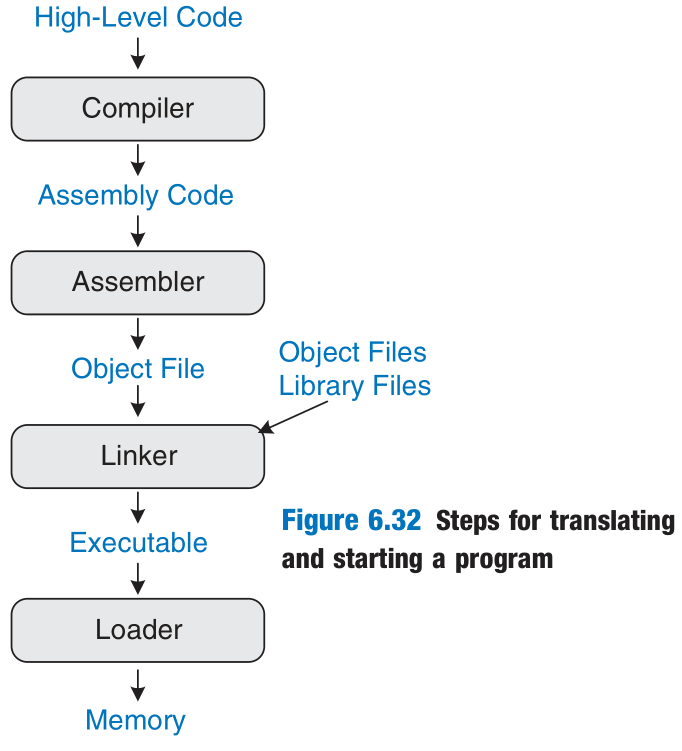

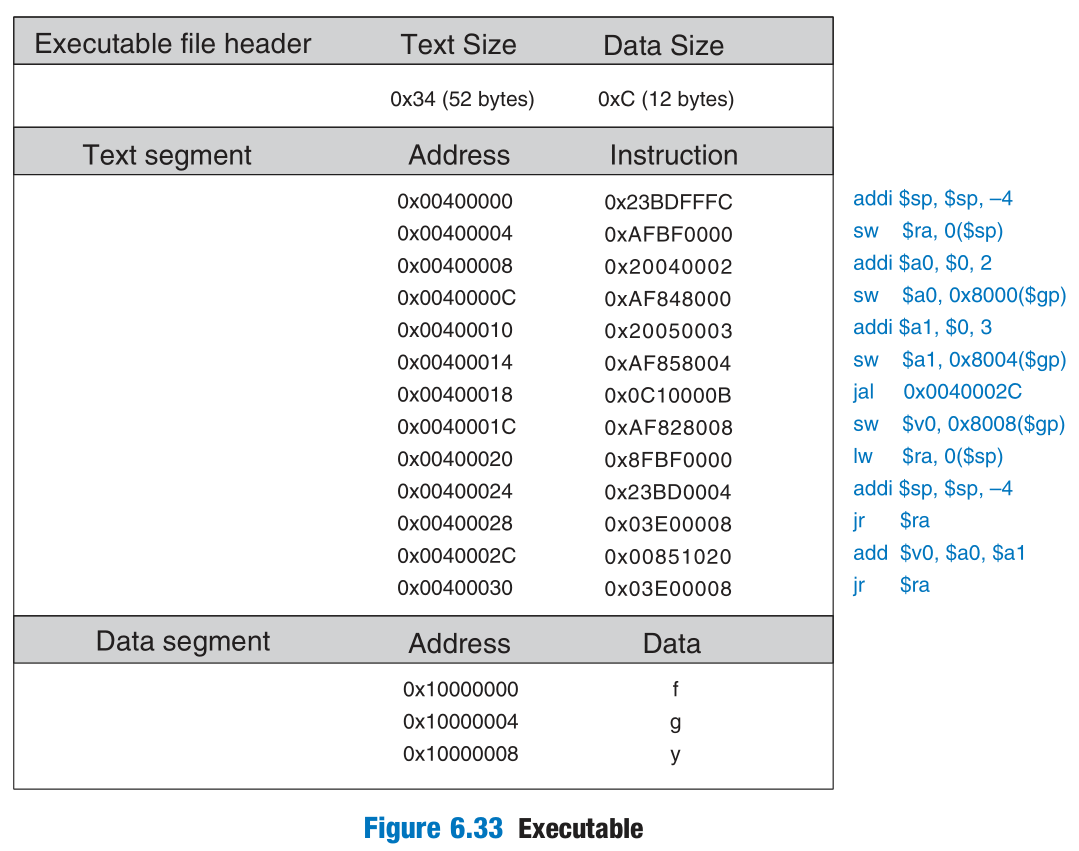

5 Compiling, Assembling, and Loading

Compilation: A compiler translates high-level code into assembly language.

Assembling: The assembler turns the assembly language code into an object file containing machine language code.

On the first pass, the assembler assigns instruction addresses and finds all the symbols, such as labels and global variable names. The names and addresses of the symbols are kept in a symbol table.

On the second pass through the code, the assembler produces the machine language code. Addresses for the global variables and labels are taken from the symbol table. The machine language code and symbol table are stored in the object file.

Linking: The job of the linker is to combine all of the object files into one machine language file called the executable.

Loading: The operating system loads a program by reading the text segment of the executable file from a storage device (usually the hard disk) into the text segment of memory. The operating system sets $gp to 0x10008000 (the middle of the global data segment) and $sp to 0x7FFFFFFC (the top of the dynamic data segment), then performs a jal 0x00400000 to jump to the beginning of the program.

Digital-Design-and-Computer-Architecture-第六章归纳

http://example.com/2022/09/05/Digital-Design-and-Computer-Architecture-第六章归纳/